FPGA VHDL Model

Diese Seite gibt eine Übersicht über die Hardware-Logik, die in den FPGA geschrieben wird. Der eigentliche VHDL-Code ist im Source Archiv enthalten. (Auf der Hauptseite im Bereich 'Downloads'.

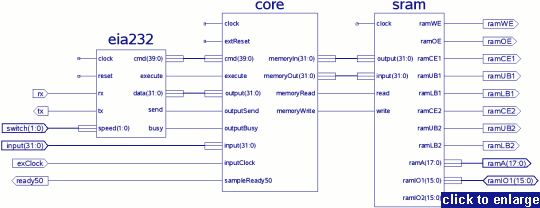

Top Level

In diesem Top Level Schema fehlen die Module Display und Clockman. Display dient nur Debugging-Zwecken und macht nichts anderes, als 'memoryOut' über Multiplexing auf dem 4-stelligen 7-Segment-Display anzuzeigen.

Das Modul Clockman erzeugt das 100MHz Taktsignal, das vom ganzen System genutzt wird.

EIA232

Erlaubt die Steuerung des Cores über eine EIA232/RS232 Schnittstelle. Das Modul (de-)serialisiert Befehle und Daten und wertet die protokollspezifischen Befehle XON/XOFF aus, die bis Version 0.6 vom Decoder (siehe Core) gehandhabt wurden.

SRAM

Übernimmt die Ansteuerung des externen SRAMs. (Adresszähler und Steuerleitungen)

Core

Der Core enthält alle "plattformunabhängigen" Module und stellt eine einfache Schnittstelle zum Analyzer zur Verfügung. Durch diese Kapselung ist der Analyzer unabhängig von der verwendeten PC-Schnittstelle und dem Speichertyp.

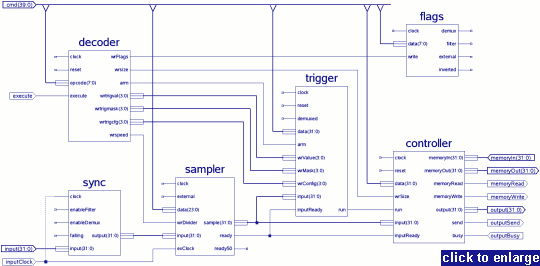

In diesem Schema fehlen einige Module: Der Trigger nutzt intern Stage und Sync nutzt intern Demux und Filter. Diese drei zusätzlichen Module werden ebenfalls beschrieben.

Controller

Steuert die Speicher- und Ausleseoperation.

Wenn kein anderer Modus aktiv ist, speichert der Controller Samples. Wenn das Startsignal empfangen wurde, speichert er weitere fwd * 4 Samples und liest danach bwd * 4 Samples aus. Durch die kontinuierliche Speicherung im Normalbetrieb ist es möglich, Daten von vor dem Auslösen des Triggers abzurufen.

Hinweis: Ausgelesene Daten von vor dem 'run'-Signal können ungültig sein, wenn der Controller kurz davor umkonfiguriert wurde und nicht ausreichend viele Daten gespeichert wurden, bevor das Signal auftrat.

Decoder

Zuständig für Befehlsausführung. Befehle werden ausgeführt, wenn 'execute' gesetzt ist.

Der Receiver hält 'opcode' und 'data' für 10 Taktzyklen. Dadurch sind alle Daten noch verfügbar, nachdem der Befehl dekodiert und an das betreffende Modul geschickt wurde.

Demux

Demultiplext 16 Eingangskanäle auf 32 Kanäle, wodurch die Samplingrate für diese Kanäle verdoppelt wird. Die oberen 16 Ausgänge sind 5ns älter als die unteren 16. Dieses Modul ist nur bei voller Geschwindigkeit (100MHz) sinnvoll. Dann lässt sich eine effektive Samplingrate von 200MHz. erreichen.

Filter

Schneller 32-Kanal Entstörfilter mit Auswertelogik in einer einzigen LUT pro Kanal. Der Filter entfernt alle Pulse, die nur für einen hablen Takt anliegen. Dadurch muss ein Puls mindestens 5-10ns lang sein, um aufgezeichnet zu werden. Diese Zeit ist ausreichend für Sampling-Raten bis 100MHz.

Flags

Flag-Register. (Die verschiedenen Flags und ihre Funktion sind in der Protokollbeschreibung aufgeführt.)

Sampler

Erzeugt Samples der Eingangsdaten indem diese mit einer programmierbaren Rate in ein Register geschrieben werden. Die Samplingrate ergibt sich wie folgt:

r = f / (d + 1)

Dabei ist r die resultierende Samplingrate, f die Frequenz des Systemtaktes und d der Wert, der im divider-Register steht.

Ab Version 0.6 kann auch ein externes Taktsignal als Sampling-Takt benutzt werden. Dazu muß external auf '1' gesetzt werden. Das divider-Register wird dann nicht beachtet.

Stage

Programmable 32 channel trigger stage. It can operate in serial and parallel mode. In serial mode any of the input channels can be used as input for the 32bit shift register. Comparison is done using the value and mask registers on the input in parallel mode and on the shift register in serial mode. If armed and 'level' has reached the configured minimum value, the stage will start to check for a match. The match and run output signal delay can be configured. The stage will disarm itself after a match occured or when reset is set.

The stage supports "high speed demux" operation in serial and parallel mode. (Lower and upper 16 channels contain a 16bit sample each.)

Matching is done using a pipeline. This should not increase the minimum time needed between two dependend trigger stage matches, because the dependence is evaluated in the last pipeline step. It does however increase the delay for the capturing process, but this can easily be compensated by software. (By adjusting the before/after ratio.)

Sync

Synchronizes input with clock on rising or falling edge and does some optional preprocessing. (See Filter and Demux above for more details.)

Trigger

Complex 4 stage 32 channel trigger.

All commands are passed on to the stages. This file only maintains the global trigger level and it outputs the run condition if it is set by any of the stages. (See Stage above for more details.)

BTW: Which application did you use to generate the Model Diagrams?

The Xilinx development tools can produce schematic diagrams like that.

In the process tree \"synthesis\" simpli double click on the process \"View RTL schematic\"